- 您现在的位置:买卖IC网 > Sheet目录1917 > DSPIC30F3013-20I/ML (Microchip Technology)IC DSPIC MCU/DSP 24K 44QFN

2011 Microchip Technology Inc.

DS39932D-page 195

PIC18F46J11 FAMILY

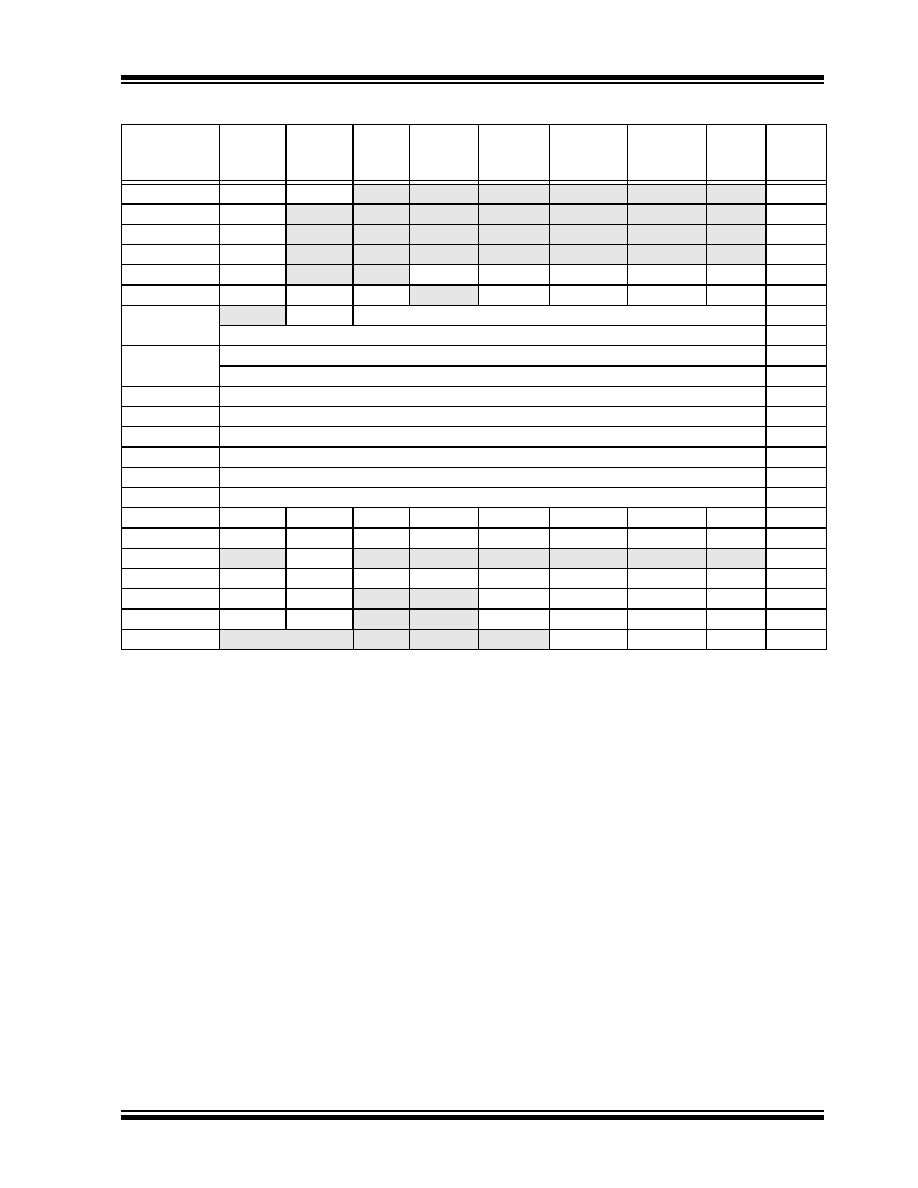

TABLE 11-2:

REGISTERS ASSOCIATED WITH PMP MODULE

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reset

Values

on Page:

INTCON

GIE/GIEH PEIE/GIEL TMR0IE

INT0IE

RBIE

TMR0IF

INT0IF

RBIF

PIR1

PMPIF(2)

ADIF

RC1IF

TX1IF

SSP1IF

CCP1IF

TMR2IF

TMR1IF

PIE1

PMPIE(2)

ADIE

RC1IE

TX1IE

SSP1IE

CCP1IE

TMR2IE

TMR1IE

IPR1

PMPIP(2)

ADIP

RC1IP

TX1IP

SSP1IP

CCP1IP

TMR2IP

TMR1IP

PMCONH(2)

PMPEN

—

ADRMUX1 ADRMUX0

PTBEEN

PTWREN

PTRDEN

PMCONL(2)

CSF1

CSF0

ALP

—

CS1P

BEP

WRSP

RDSP

PMADDRH(1,2)/

—

CS1

Parallel Master Port Address High Byte

PMDOUT1H(1,2) Parallel Port Out Data High Byte (Buffer 1)

PMADDRL(1,2)/ Parallel Master Port Address Low Byte

PMDOUT1L(1,2) Parallel Port Out Data Low Byte (Buffer 0)

PMDOUT2H(2)

Parallel Port Out Data High Byte (Buffer 3)

PMDOUT2L(2)

Parallel Port Out Data Low Byte (Buffer 2)

PMDIN1H(2)

Parallel Port In Data High Byte (Buffer 1)

PMDIN1L(2)

Parallel Port In Data Low Byte (Buffer 0)

PMDIN2H(2)

Parallel Port In Data High Byte (Buffer 3)

PMDIN2L(2)

Parallel Port In Data Low Byte (Buffer 2)

PMMODEH(2)

BUSY

IRQM1

IRQM0

INCM1

INCM0

MODE16

MODE1

MODE0

PMMODEL(2)

WAITB1

WAITB0 WAITM3 WAITM2

WAITM1

WAITM0

WAITE1

WAITE0

PMEH(2)

—PTEN14

—

PMEL(2)

PTEN7

PTEN6

PTEN5

PTEN4

PTEN3

PTEN2

PTEN1

PTEN0

PMSTATH(2)

IBF

IBOV

—

IB3F

IB2F

IB1F

IB0F

PMSTATL(2)

OBE

OBUF

—

OB3E

OB2E

OB1E

OB0E

PADCFG1

—

RTSECSEL1 RTSECSEL0 PMPTTL

Legend:

— = unimplemented, read as ‘0’. Shaded cells are not used during PMP operation.

Note 1:

The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and

addresses, but have different functions determined by the module’s operating mode.

2:

These bits and/or registers are only available in 44-pin devices.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F4011-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F4013-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F5013-30I/PT

IC DSPIC MCU/DSP 66K 80TQFP

DSPIC30F5015-30I/PT

IC DSPIC MCU/DSP 66K 64TQFP

DSPIC30F6010-20E/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6010A-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6013A-30I/PF

IC DSPIC MCU/DSP 132K 80TQFP

DSPIC30F6014-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

相关代理商/技术参数

dsPIC30F3013-20I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 28LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC30F3013-20I/SP

功能描述:数字信号处理器和控制器 - DSP, DSC 28LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/ML

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SO

制造商:Microchip Technology Inc 功能描述:IC DSC 16BIT 24KB 40MHZ 5.5V SOIC-28

DSPIC30F3013-30I/SP

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SP

制造商:Microchip Technology Inc 功能描述:16-Bit Digital Signal Controller

dsPIC30F3013T-20E/ML

功能描述:数字信号处理器和控制器 - DSP, DSC 44LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT